科研项目

潘彪老师近五年主持国家自然科学基金青年项目一项,科技部国家重点研发计划子课题一项,获批北航青年拔尖人才计划一项,企业横向项目三项。此外,潘彪老师及其所领导的翼动芯生课题组围绕自旋存储器件及存算一体电路方面开展了大量研究,累计完成4次流片。

项目相关

在国家自然科学基金青年项目-“磁性斯格明子脉冲神经网络电路研究”支持下,开展基于斯格明子的类脑计算芯片研究。与韩国科学技术学院Woo教授团队一同开展了基于斯格明子的人工神经突触的研究,在国际上首次成功观察到基于斯格明子的人工神经突触,并成功应用于MNIST手写数字识别等智能识别任务,相关研究成果发表于在Nature Electronics上。为搭建完整的脉冲神经网络,同时开展基于斯格明子的人工神经元研究,以通讯作者在Applied Science上发表论文1篇,以第一作者在国际电路领域会议ISCAS上发表会议论文2篇。在北航青年拔尖人才计划支持下,开展基于自旋忆阻器的类脑计算芯片研究。为打破磁隧道结器件固有的单比特存储特征,潘彪老师开展具有可控多阻态的自旋忆阻器及基于多比特存储特性的类脑计算电路和计算架构研究,以共同一作和第一作者在Advanced Science、IEEE TCAS-II和IEEE Journal of the Electron Devices Society各发表论文一篇。

在科技部重点研发计划-“新型自旋轨道矩材料与高性能存内计算器件”和国家自然科学基金面上项目-“基于自旋轨道矩器件的存内计算异构芯片与系统研究”项目支持下,潘彪老师开展基于自旋电子器件的存算一体芯片研究。针对当前自旋存算一体技术中所存在的器件集成和计算架构等问题,以通讯作者在IEEE TCAS-II、IEEE TETC和ISCAS上各发表论文一篇,申请并授权发明专利2项,并已完成科研成果转化。在两项企业联合基金支持下,开展基于RISC-V+存算一体的芯片研究,在55nm工艺下完成两次流片验证,以通讯作者在IEEE TCAS-I和Applied Science上各发表论文2篇,申请发明专利5项。

流片相关

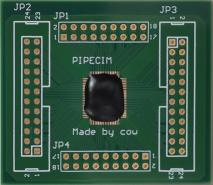

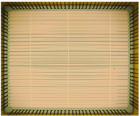

自旋存算一体芯片流片-华山&恒山芯片:2019年开始,潘彪老师及其课题组开展了基于自旋存储器的存算一体芯片研究。于2021年完成了一款基于180nm STT-MRAM的模拟存算一体芯片-华山的设计并进行了流片验证,如表1第一列所示。华山芯片使用了高可靠性的STT-MRAM作为非易失性主存,实现了1.8 TOPS/W的高计算能效比,证明了自旋存储器在存算一体技术中的应用潜力,特别是在近似计算范式的背景下。2022年,在科技部重点研发计划和项目支持下,面向当前自旋存算一体技术中所存在的器件集成和计算架构等问题,开展了基于180nm SOT-MRAM的模拟存算一体芯片-恒山的研究并完成了流片验证,如表1第二列所示。恒山芯片以读写更加可控的SOT-MRAM器件为基础,能够支持两种AI应用验证,从而为自旋存算一体芯片在AI领域的应用提供了直接的技术支撑和实践依据。

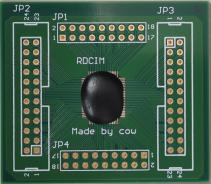

SRAM模拟存算一体芯片流片-嵩山芯片:潘彪老师在两项企业联合基金支持下,开展了基于RISC-V+存算一体的芯片研究。于2022年完成了一款基于55nm RISC-V+SRAM的模拟存算一体芯片-嵩山的研究并进行了流片验证,包括基于SRAM的模拟存算一体电路方案及定制化RISC-V扩展指令集设计,如表1第三列所示。嵩山芯片面向端侧神经网络部署,利用多级流水和数字接口的方式提高了存算一体芯片的灵活度,具有2KB的存储容量,实现了44.6 TOPS/W的计算能效。该芯片属于基于SRAM的存算一体电路方案及定制化RISC-V扩展指令集设计方面的研究。

SRAM数字存算一体芯片流片-衡山芯片: 在安徽省重点研发计划-“面向AIoT端侧应用场景的RISC-V+存算一体高能效计算芯片”项目支持下,潘彪老师及其课题组于2023年完成了一款55nm RISC-V+SRAM的数字存算一体芯片-衡山芯片并进行了流片验证。该芯片具有64KB的存储容量,在8比特精度下峰值计算能效可达12TOPS/W,如表1第四列所示。该工作以数字存算一体作为加速器架构降低了系统延时,并初步探索了存算一体阵列与数字逻辑的耦合设计,展示了数字存算一体加速器架构的有效性,表明了其在减少系统延时和提高计算效率方面的贡献。

表1 翼动芯生课题组近三年完成的代表性流片工作

评论区